# High-Performance *Ka*-Band and *V*-Band HEMT Low-Noise Amplifiers

K. H. GEORGE DUH, MEMBER, IEEE, PANE-CHANE CHAO, SENIOR MEMBER, IEEE, PHILLIP M. SMITH, SENIOR MEMBER, IEEE, LUKE F. LESTER, BENJAMIN R. LEE, JAMES M. BALLINGALL, MEMBER, IEEE, AND MING-YIH KAO, MEMBER, IEEE

**Abstract** — Quarter-micron-gate-length high electron mobility transistors (HEMT's) developed in our laboratory have exhibited state-of-the-art low-noise performance at millimeter-wave frequencies, with minimum noise figures of 1.2 dB at 32 GHz and 1.8 dB at 60 GHz. At *Ka*-band, two-stage and three-stage HEMT low noise amplifiers have demonstrated noise figures of 1.7 and 1.9 dB, respectively, with associated gains of 17.0 and 24.0 dB at 32 GHz. At *V*-band, two-stage and three-stage HEMT amplifiers yielded noise figures of 3.2 and 3.6 dB, respectively, with associated gains of 12.7 and 20.0 dB at 60 GHz. The 1 dB gain compression point of all the amplifiers is greater than +6 dBm. These results clearly show the potential of short-gate-length HEMT's for high-performance millimeter-wave receiver applications.

## I. INTRODUCTION

**T**RADITIONALLY, room-temperature low-noise receiver front ends in the millimeter-wave frequency region have been limited to mixer front ends followed by a high-gain IF amplifier or a parametric amplifier front end [1]–[3]. Recently, heterostructure transistor technology has advanced very rapidly in both the high-speed and high-frequency areas. High electron mobility transistors (HEMT's) have shown superb low-noise results well into the millimeter-wave frequency range [4], surpassing conventional GaAs MESFET's in low-noise performance. Low-noise amplifiers (LNAs) implemented with HEMT's now present a strong challenge even to cooled parametric amplifier front ends. HEMT LNA's are also suitable for monolithic integration and have a great potential for low-cost receivers. HEMT amplifiers have been demonstrated at *Ka*-band [5]–[7] and *V*-band [8]–[10]. In this paper, we report state-of-the-art *Ka*-band and *V*-band LNA performance.

## II. LOW-NOISE HEMT'S

For a field effect transistor (FET), the minimum noise figure can be approximated by [11]

$$F_{\min} \approx 1 + 4\pi f C_g \sqrt{\beta (R_s + R_g) \frac{I_{ds}}{g_m^2}} = 1 + A \sqrt{\frac{I_{ds}}{g_m'^2}} \quad (1)$$

where  $C_g$  is the active gate capacitance and  $\beta$  is an

Manuscript received May 4, 1988; revised July 25, 1988. This work was supported in part by JPL under Contract 957352. The *V*-band development was performed under a GE internal R & D program.

The authors are with the Electronics Laboratory, General Electric Company, Syracuse, NY 13221.

IEEE Log Number 8823765.

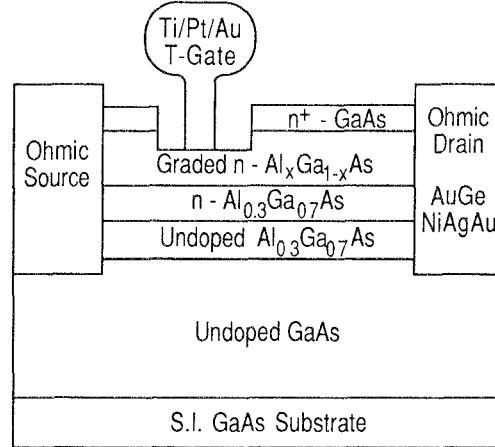

Fig. 1. Cross-sectional view of a  $0.25 \mu\text{m}$  AlGaAs/GaAs HEMT device.

empirical constant, which is the ratio of the channel thermal noise spectrum to the saturated drain current. The quantity  $g_m$  is the intrinsic transconductance while  $g_m'$  is the extrinsic transconductance. It is necessary to have high-purity material and low parasitic resistances  $R_s$  and  $R_g$  in order to obtain good low-noise devices. It is also necessary to have high transconductance,  $g_m$ , at the operating bias condition while keeping  $C_g$  low. These requirements can be achieved by proper layer structure design and processing. Fig. 1 schematically illustrates the cross section of the HEMT devices. The  $0.25 \mu\text{m}$  devices were fabricated on selectively doped AlGaAs/GaAs heterostructures grown by molecular beam epitaxy (MBE).  $R_s$  is minimized by 1) aligning the gate close to the source using electron-beam lithography and 2) employing a graded Al composition AlGaAs region and utilizing rapid thermal annealing to obtain very low ohmic contact resistance (the transfer resistance is between  $0.03$  and  $0.1 \Omega \cdot \text{mm}$ ).  $R_g$  is greatly reduced by using a large cross section T-shaped gate [12] (dc end-to-end resistance is less than  $80 \Omega/\text{mm}$ ).

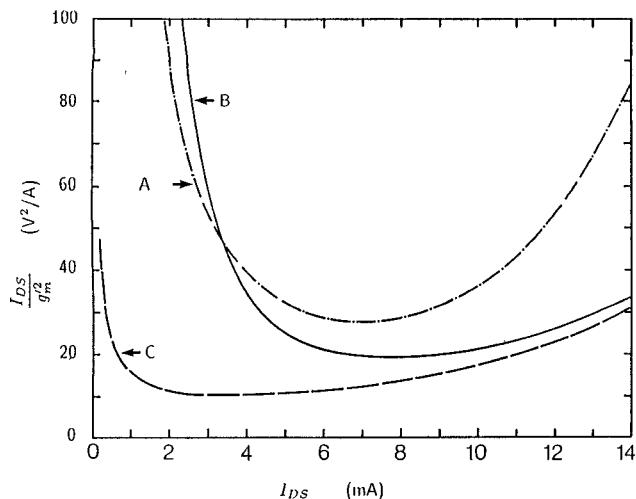

The last approximation of (1) is made by separating out the quantities that are strong functions of gate bias [13] with the purpose of using the expression to effectively select the low-noise devices for amplifier applications. Fig. 2 illustrates the  $I_{ds}/g_m'^2$  versus  $I_{ds}$  relationship of the devices from three wafers with the same layer structure. An advantage of this plot is that it shows where to operate

Fig. 2. The  $I_{ds}/g_m'^2$  versus  $I_{ds}$  relationship of devices from wafers A, B, and C.

TABLE I

SUMMARY OF DEVICE CHARACTERISTICS FROM WAFERS A, B, AND C

| WAFER #                                            | A    | B    | C    |

|----------------------------------------------------|------|------|------|

| 1 GHz thermal noise<br>$\theta = \beta I_{ds}/g_m$ | 1.1  | 1.0  | 0.8  |

| $I_{ds}/g_m'^2$                                    | 28   | 19.5 | 10   |

| $C_{go}$ (PF)<br>150 $\mu\text{m}$ wide            | 0.24 | 0.20 | 0.16 |

| 18 GHz NF (dB)                                     | 1.3  | 1.2  | 0.7  |

| 60 GHz NF (dB)                                     | 3.3  | 2.7  | 1.8  |

Thermal noise coefficient,  $\theta$ , is defined as the ratio of thermal channel current noise spectrum to  $4kT\Delta f g_m$  [17].

the device to obtain minimum noise. It is to be expected from this figure that devices from wafer C should exhibit the lowest noise figure. It is also found from low-frequency noise measurements that devices from wafer C exhibit extremely low  $1/f$  and thermal noise, indicating good material quality with very low trap density. As summarized in Table I, the devices from wafer C showed the best low-noise performance, followed by those from wafer B, and then those from wafer A.

Table II displays the 0.25  $\mu\text{m}$  AlGaAs/GaAs HEMT noise performance from 8 to 60 GHz. These HEMT's gave minimum noise figure of 1.2 dB with associated gain of 10 dB at 32 GHz and 1.8 dB noise figure with 6.4 dB gain

TABLE II

ROOM-TEMPERATURE NOISE PERFORMANCE OF 0.25  $\mu\text{m}$  HEMT'S

| Frequency (GHz) | NF (dB) | Ga (dB) | $F_\infty$ (dB) |

|-----------------|---------|---------|-----------------|

| 8               | 0.4     | 15.2    | 0.41            |

| 18              | 0.7     | 13.8    | 0.73            |

| 32              | 1.2     | 10.0    | 1.31            |

| 60              | 1.8     | 6.4     | 2.22            |

$$F_\infty = F + \frac{F-1}{G} + \frac{F-1}{G^2} + \dots = \frac{FG-1}{G-1}$$

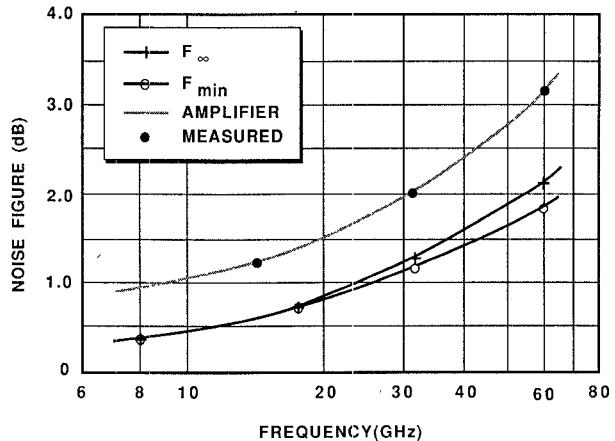

Fig. 3. Noise figure achievable using present 0.25  $\mu\text{m}$  HEMT's.

at 60 GHz—the best device results yet reported for any microwave transistor.  $F_\infty$  in Table II is defined as the noise figure of an infinite chain of cascaded single-stage amplifiers. It is a useful figure of merit that closely approximates the noise figure attainable in a multistage, high-gain ( $>15$  dB) amplifier. In Fig. 3, we have plotted the frequency dependence of  $F_\infty$ . In addition, if one assumes realistic transition losses, the upper curve represents the noise figure of multistage, high-gain amplifiers as they will be used in a system. The measured points are the amplifiers that have been achieved with the current devices. These are discussed in the following sections.

Results of reliability testing for low-noise AlGaAs/GaAs HEMT's are encouraging [4]. MTTF of  $10^6$  hours is expected at a channel temperature of 150°C based on the measured activation energy of 1.6 eV.

### III. Ka-BAND AMPLIFIERS

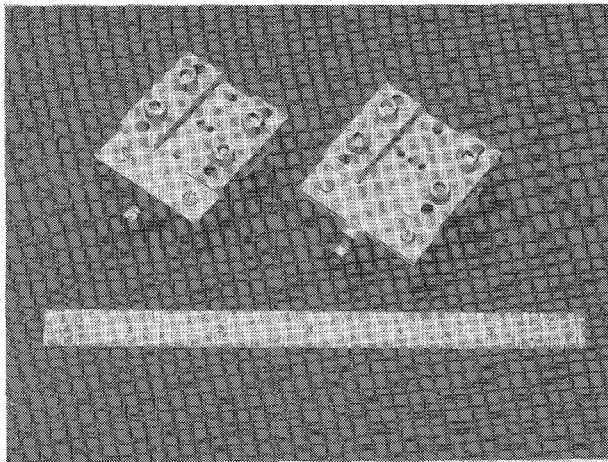

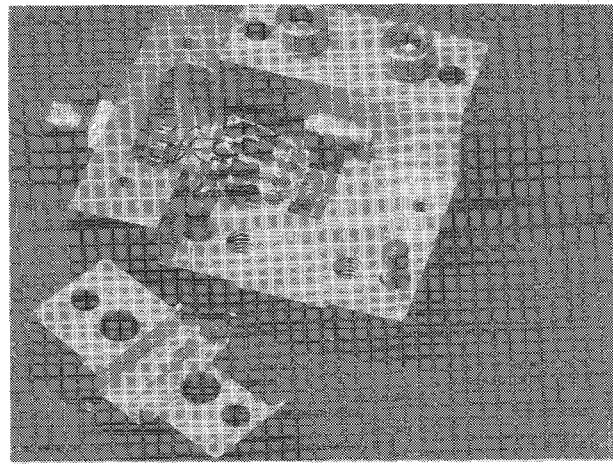

Fig. 4 is a photograph of the Ka-band two-stage and three-stage HEMT LNA's. A stepped ridge to microstrip transition was utilized in the amplifier. The amplifier design was based on 0.25  $\times$  75  $\mu\text{m}$  HEMT's. The input and output networks included the waveguide to microstrip transitions. The device equivalent circuit model was ob-

Fig. 4. Ka-band two-stage and three-stage HEMT LNA's.

tained using Super-Compact to fit  $S$  parameters measured at the low-noise bias condition from 2 to 20 GHz. We then selected the equivalent circuit topology and determined some element values for the Ka-band LNA design based upon good agreement between calculated and measured millimeter-wave gain performance [14]. The input, output, and interstage matching circuits were designed on 10 mil quartz substrates with TaN thin-film resistors and TiW/Au metallization. The edge-coupled symmetric microstrip dc blocking circuit (two finger) was used to provide low-loss dc isolation and improve stability out of band, functioning as a bandpass filter.

The LNA fixture and dc bias circuits were designed to be compatible with cryogenic operation, since the ultimate application (deep space exploration and radio astronomy receivers) would require cooling. Diode protection was included in both the gate and drain bias circuits. LED's are mounted on top of the cover, directly above the devices (in the holes shown in Fig. 4) so that the HEMT's can be illuminated. This is done because previous experience with HEMT's has shown that illumination can improve the noise performance at a cryogenic temperature of 12 K [15], [16].

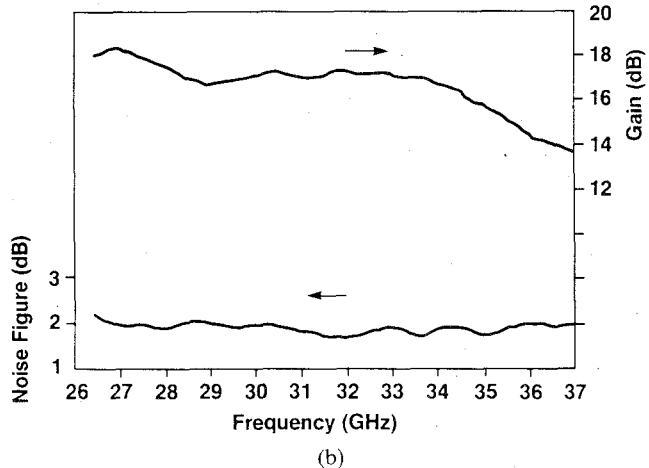

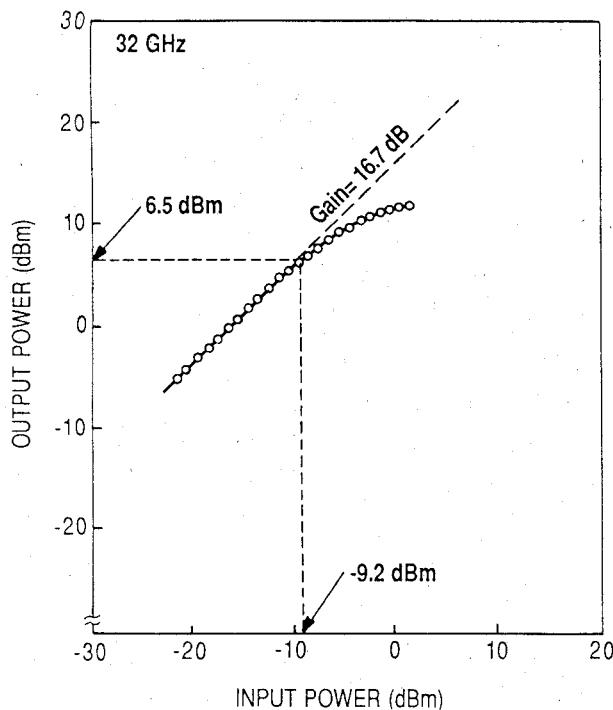

The two-stage amplifier and its broad-band performance are shown in Fig. 5. The amplifier exhibited an average noise figure of 2 dB from 26.5 GHz to 37 GHz. At 32 GHz, it demonstrated a noise figure of 1.7 dB with 17 dB associated gain. The gain is  $17.0 \pm 0.5$  dB from 29 to 34 GHz. With an external waveguide isolator to minimize input  $VSWR$ , the noise figure and the gain degraded by only 0.3 dB across the band. The gain compression characteristic of the amplifier is shown in Fig. 6. Typically, the output power of the LNA is greater than +6 dBm at the 1 dB compression point.

Fig. 7 shows the three-stage amplifier and its noise/gain performance from 26.5 to 37 GHz. The LNA achieved a gain level of  $23.5 \pm 1.5$  dB from 26.5 to 34 GHz. The noise figure exhibits a flat response, and is 2 dB from 29 to 36 GHz. At the design frequency, 32 GHz, the amplifier yields a noise figure of 1.9 dB with gain of 24.0 dB.

(a)

Fig. 5. Ka-band two-stage HEMT LNA. (a) Amplifier assembly. (b) Measured noise and gain characteristics.

#### IV. V-BAND AMPLIFIERS

$E$ -field probes were used for the  $V$ -band waveguide to microstrip transition. Microstrip circuits and adjustable backshorts were also included in the fixture to optimally match the radiation impedance to  $50 \Omega$  to achieve best transition performance. The  $V$ -band fixture with a  $50 \Omega$  through line containing two edge-coupled lines (necessary to provide dc blocking) has a measured insertion loss of 1 dB with an input return loss of approximately 20 dB in the test band.

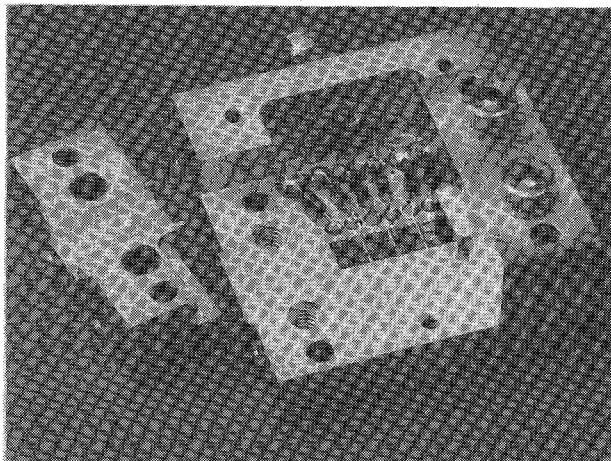

A photograph of the two-stage and three-stage HEMT amplifiers is shown in Fig. 8. The single-ended amplifier stages are cascaded directly. HEMT devices with dimensions  $0.25 \times 50 \mu\text{m}$  were selected for the  $V$ -band LNA work on the basis of a trade-off between optimum impedance matching, power handling capability, intermodulation distortion, and power dissipation. The gate and drain bias circuits, which consisted of high- and low-impedance quarter-wavelength transmission lines, bonding wires, chip capacitors, and resistors, were designed to be unconditionally stable from low frequency (megahertz range) to 100 GHz.

Fig. 6. Output power versus input power for *Ku*-band two-stage HEMT LNA.

Fig. 7. *Ku*-band three-stage HEMT LNA. (a) Amplifier assembly. (b) Measured noise and gain characteristics.

Fig. 8. *V*-band two-stage and three-stage HEMT LNA's.

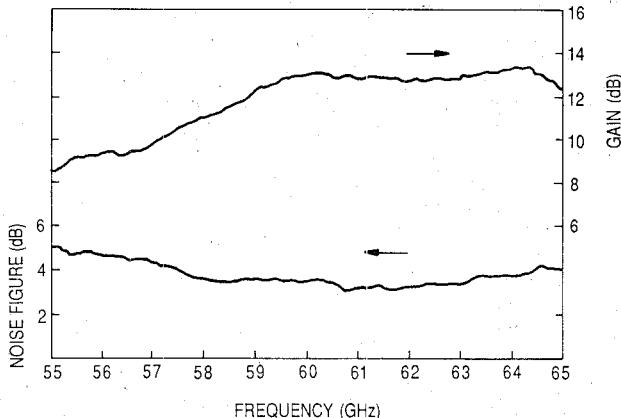

Fig. 9. Measured noise and gain characteristics of *V*-band two-stage HEMT LNA.

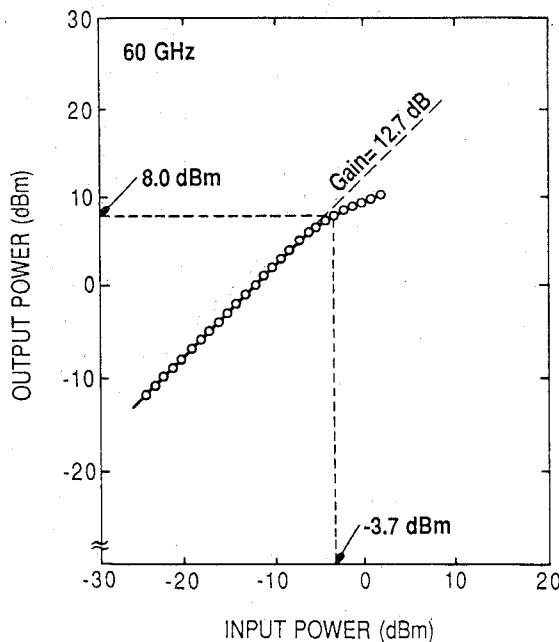

The two-stage LNA performance from 55 to 65 GHz is shown in Fig. 9. The minimum noise figure is 3.2 dB with 12.7 dB gain at 61 GHz. The flat gain response of the LNA is  $12.7 \pm 0.5$  dB from 58 GHz to 65 GHz with a noise figure of less than 4 dB across the band. The input return loss of the LNA is approximately 10 dB from 56 GHz to 64 GHz, which is significantly better than that of a GaAs FET LNA. This is because the optimum source impedances of HEMT's for minimum noise and for gain match are closer than those of the FET's. The noise source used in this measurement was calibrated by the hot/cold method. Gain compression measurements were performed at 60 GHz, as shown in Fig. 10. The 1 dB compression point is +8 dBm. At maximum output power (+11 dBm), the two-stage amplifier has a power-added efficiency of 20 percent with 9 dB gain. The high efficiency is attributed to high device transconductance and sharp pinch-off characteristics.

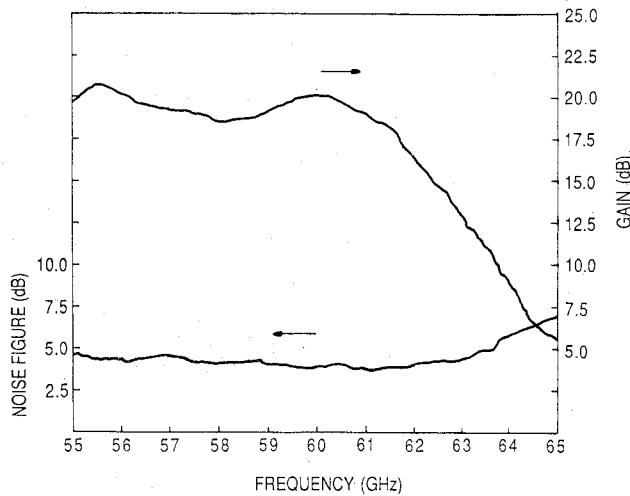

The three-stage LNA was designed with  $50 \mu\text{m}$  devices in the first and second stages, and a  $75 \mu\text{m}$  device in the third stage. The amplifier performance was optimized to cover 55 to 62 GHz, as shown in Fig. 11. The gain level is  $19.0 \pm 2.0$  dB, with a noise figure of less than 4.5 dB across the band. The LNA exhibited a noise figure of 3.6 dB with

Fig. 10. Output power versus input power for  $V$ -band two-stage HEMT LNA.

Fig. 11. Measured noise and gain characteristics of  $V$ -band three-stage HEMT LNA.

gain of 20.0 dB at 60 GHz. The 1 dB compression point of the amplifier is +7.0 dBm.

## V. CONCLUSION

We have demonstrated state-of-the-art  $Ka$ -band and  $V$ -band HEMT low-noise amplifier performance using our 0.25  $\mu\text{m}$  HEMT devices. The results clearly show their great potential for millimeter-wave low-noise receiver applications. Further advances in transistor technology [18] will lead to improved performance at all frequencies and will also make it possible to develop transistor amplifiers at frequencies above 100 GHz. In the future, HEMT's will continue to be used in high-performance hybrid amplifiers such as those reported here, as well as in applications requiring low-cost, large-quantity MMIC's, and will have a significant impact on component/system design and performance.

## ACKNOWLEDGMENT

The authors acknowledge the support of A. W. Swanson and W. J. Butler. Useful discussions with S. M. J. Liu, M. W. Pospieszalski, S. Weinreb, J. J. Bautista, and S. Petty are gratefully acknowledged.

## REFERENCES

- [1] S. Weinreb, "Low-noise technology, 1982 state-of-the-art," in *1982 IEEE MTT-S Dig.*, pp. 10-12.

- [2] M. McColl and H. J. Wintrob, "Microwave receiver technology for space systems," in *Proc. 1983 IEEE National Telesystems Conf.*, pp. 39-43.

- [3] W. R. Vincent, "Radio noise and interference," in *Reference Data for Engineers: Radio, Electronics, Computer, and Communications*, 7th ed., E. C. Jordan, Ed. Indianapolis, IN: Howard W. Sams, 1985, ch. 34, p. 34-3.

- [4] P. M. Smith, P. C. Chao, K. H. G. Duh, L. F. Lester, B. R. Lee, and J. M. Ballagall, "Advances in HEMT technology and applications," in *1987 IEEE MTT-S Dig.*, pp. 749-752.

- [5] J. M. Schellenberg, M. V. Maher, S. K. Wang, K. G. Wang, and K. K. Yu, "35 GHz low noise HEMT amplifier," in *1987 IEEE MTT-S Dig.*, pp. 441-442.

- [6] M. A. G. Upton, P. M. Smith, P. C. Chao, and K. H. G. Duh, "HEMT low-noise amplifier for  $Ka$ -band," in *1987 IEEE MTT-S Dig.*, pp. 1007-1010.

- [7] M. Sholley, J. Berenz, A. Nichols, K. Nakano, R. Sawires, and J. Abell, "36.0-40.0 GHz HEMT low noise amplifier," in *1985 IEEE MTT-S Dig.*, pp. 555-558.

- [8] J. Berenz, K. Nakano, T.-I. Hsu, and J. Goel, "HEMT 60 GHz amplifier," *Electron. Lett.*, vol. 21, pp. 1028-1029, 1985.

- [9] K. H. G. Duh, P. C. Chao, P. M. Smith, L. F. Lester, and B. R. Lee, "60 GHz low-noise high-electron-mobility transistors," *Electron. Lett.*, vol. 22, pp. 647-649, 1986.

- [10] W. Yau, E. T. Watkins, S. K. Wang, K. Wang, and B. Klatskin, "A four stage  $V$ -band MOCVD HEMT amplifier," in *1987 IEEE MTT-S Dig.*, pp. 1015-1018.

- [11] A. F. Podell, "A functional GaAs FET noise model," *IEEE Trans. Electron Devices*, vol. ED-28, p. 511, 1981.

- [12] P. C. Chao, P. M. Smith, S. C. Palmateer, and J. C. M. Hwang, "Electron-beam fabrication of GaAs low-noise MESFET's using a new tri-layer resist technique," *IEEE Trans. Electron Devices*, vol. ED-22, pp. 1042-1046, 1985.

- [13] K. H. G. Duh *et al.*, "Ultra-low-noise characteristics of millimeter-wave high electron mobility transistors," to be submitted to *IEEE Electron Device Lett.*

- [14] K. H. G. Duh *et al.*, "32 GHz cryogenically cooled HEMT low-noise amplifiers," to be submitted to *IEEE Trans. Electron Devices*.

- [15] M. W. Pospieszalski *et al.*, "Noise parameters and light sensitivity of low-noise high-electron-mobility transistors," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 218-223, 1986.

- [16] K. H. G. Duh *et al.*, "Ultra-low-noise cryogenic high-electron-mobility transistors," *IEEE Trans. Electron Devices*, vol. ED-35, pp. 249-256, 1988.

- [17] S. M. Liu *et al.*, "A comparison of low-and high frequency noise spectra of 0.1 micron gate-length conventional, pseudomorphic, and planar-doped MODFET structures," in *1987 IEDM*, paper 17.2.

- [18] P. C. Chao *et al.*, "High performance 0.1  $\mu\text{m}$  gate-length planar-doped HEMTs," in *1987 IEDM*, paper 17.1.

+

**K. H. George Duh** (S'79-M'84) received the B.S.E.E. degree from National Taiwan University, Taipei, Taiwan, in 1977, the M.S.E.E. degree from Syracuse University, Syracuse, NY, in 1981, and the Ph.D. degree in electrical engineering from University of Minnesota, Minneapolis, in 1984.

From 1983 to August 1984, he was with the GaAs Microelectronics Department, Honeywell Corporate Technology Center, Minneapolis, MN, where he worked on NASA 30 GHz monolithic

receive module designs. He joined the General Electric Electronics Laboratory in September 1984, where he is currently a Principal Staff Engineer of the Advanced Materials and Devices Laboratory. His primary area of responsibility is ultra-sub-micron low-noise device design, development, and characterization for both cryogenic and room-temperature applications from 1 to 100 GHz. He is also interested in high-performance hybrid/monolithic HEMT circuit development for microwave and millimeter-wave applications.

★

**Pane-Chane Chao** (S'80-M'82-SM'88) received the B.S. and M.S. degrees in electrical engineering from National Cheng-Kung University, Taiwan, Taiwan, in 1975 and 1977, respectively, and the Ph.D. degree, also in electrical engineering, from Cornell University, Ithaca, NY, in 1982.

In 1982, he joined the Electronics Laboratory, General Electric Company, Syracuse, NY. His primary responsibilities included the electron-beam lithography process development for frequencies up to 94 GHz. In 1986, he became

Manager of the Advanced Lithographic Processes Group, and is responsible for the entire process development of 0.25 and 0.1  $\mu\text{m}$  high-performance HEMT's and HEMT-based MMIC's at GE.

Dr. Chao has been a visiting scientist of the National Nanofabrication Facility at Cornell University since 1982. He has published approximately 50 technical papers in the area of microwave and millimeter-wave semiconductor devices and circuits. He is also the recipient of the 1986 IEEE best paper award. Dr. Chao is a member of the American Physical Society.

★

**Phillip M. Smith** (S'80-M'82-SM'88) received the B.S., M.S., and Ph.D. degrees in electrical engineering in 1976, 1978, and 1982, respectively, from Cornell University, Ithaca, NY.

He has been at the General Electric Electronics Laboratory in Syracuse, NY, since 1981, involved in the development of high-frequency devices and circuits. From 1981 to 1984, he spent a portion of his time as a visiting scientist at Cornell University. From 1984 to 1986 he was a Principal Staff Engineer, contributing to the de-

sign and testing of a number of devices, including HEMT's, GaAs FET's and mixer diodes. He has established capabilities for accurately characterizing device S parameter, power, and noise properties. He is currently Manager of the Advanced Devices Subsection, focusing on the development of low-noise and low-power HEMT's and associated circuit applications (both hybrid and monolithic) at frequencies ranging from 1 to 94 GHz.

★

length FET's.

**Luke F. Lester** was born in Summit, NJ, in 1962. He received the B.S. degree in engineering physics from Cornell University in 1984.

Since 1985, he has worked as a Process Engineer for General Electric's Electronics Laboratory in Syracuse, NY. His work there has involved primarily 0.25  $\mu\text{m}$  HEMT process and design. He is currently enrolled as a M.S./Ph.D. student in electrical engineering at Cornell University, where he is researching III-V heterojunction power devices and extremely short gate

**Benjamin R. Lee** received the Sc.B. degree in chemistry from Brown University, Providence, RI, in 1981, the B.S.E. degree in materials and metallurgical engineering from the University of Michigan, Ann Arbor, in 1983, and the M.S. degree in solid state science and technology from Syracuse University, Syracuse, NY, in 1987.

He joined GE's Electronics Laboratory, Syracuse, NY, in 1984 as a Material Engineer responsible for MBE growth and development of III-V semiconductors. He has grown HEMT layers that have yielded state-of-the-art performance in noise figure, bandwidth, and power density at 60 GHz. He also implemented growth of double-heterojunction pseudomorphic HEMT's which have demonstrated record millimeter-wave power performance (density and efficiency) at 35 GHz and 60 GHz. Currently, he is a HEMT Process Engineer in GE's Advanced Lithographic Processes group.

★

**James M. Ballingall** (M'86) received the B.S. degree in engineering physics from the University of California at Berkeley in 1978 and the Ph.D. degree in applied physics from Cornell University, Ithaca, NY, in 1982 where he began his studies in molecular beam epitaxy (MBE).

As a scientist at McDonnell Douglas Research Laboratories, he and his collaborators grew the first single crystalline HgTe-CdTe superlattices on GaAs substrates. In 1986, he joined the General Electric Electronics Laboratory as Manager of Epitaxial Technology, where he has established new programs in  $\text{In}_x\text{Ga}_{1-x}\text{As}$  HEMT materials technology and metal-organic molecular beam epitaxy (MOMBE).

★

**Ming-Yih Kao** (S'84-M'86) received the B.S. degree in physics from National Tsing Hua University, Hsin-Chu, Taiwan, in 1978, and the M.S. degree in electrical engineering from University of Massachusetts at Amherst in 1986.

Prior to his graduate studies, he was a Process Engineer and, later, Head of the Process Engineering Group at Advanced Devices Technology Inc., where he was responsible for the process development of the first commercial power DMOSFET and bipolar transistor in Taiwan.

Since 1987, he has been with GE's Electronics Laboratory as a Submicron Process Engineer working on the development and fabrication of HEMT's and HEMT MMIC's.